How fast does a pin diode switch respond

PIN Diode Switch Response Speed Analysis

Critical Performance Parameters and Optimization Strategies

1. Basic Mechanism and Response Time Components

PIN diodes feature a wide intrinsic (I) layer between P and N regions, which stores charge carriers (electrons and holes) when forward-biased. When switching from the on state (conducting) to the off state (blocking), the stored charge must be removed through reverse biasing, a process that determines the turn-off delay.

Usually ranges from nanoseconds to microseconds, dominated by the carrier recombination or extraction rate in the I-layer.

Often sub-nanosecond or within tens of nanoseconds, limited by the time required to establish a stable current.

2. Key Factors Affecting Response Speed

Thinner I-layers reduce charge storage, enabling faster switching (e.g., high-frequency PIN diodes with sub-micron I-layers may achieve <10 ns turn-off).

Lower doping in the I-layer prolongs carrier lifetime, slowing down recombination and degrading response speed.

Reverse bias voltage: Higher reverse voltage accelerates carrier extraction, reducing turn-off time. For example, a 50 V reverse bias may shorten turn-off from 1 μs to 100 ns in some devices.

Forward bias current: Sufficient forward current ensures full carrier injection for low on-resistance but increases stored charge, potentially delaying turn-off.

Series resistance: Higher resistance in the biasing circuit limits current change rates, slowing switching.

Parasitic capacitances: Junction capacitance (Cj) and stray inductance in the package or PCB can introduce RC or LC time constants, especially at high frequencies.

Higher temperatures accelerate carrier recombination, reducing turn-off time. However, excessive heat may degrade device reliability or alter doping profiles.

3. Typical Performance Ranges

| Application | Frequency Range | Turn-off Time | Turn-on Time |

|---|---|---|---|

| Low-frequency applications | DC to 1 MHz | 1–10 μs | <1 μs |

| High-frequency RF/microwave | 1–10 GHz | 10–100 ns | <5 ns |

| Example: 5 GHz radar system | 5 GHz | <20 ns | Sub-nanosecond |

4. Trade-offs and Optimization Strategies

- Speed vs. Power Handling: Faster switches often have thinner I-layers, reducing power dissipation but limiting voltage/current ratings.

- Package Design: Surface-mount (SMT) or chip-scale packages minimize parasitic inductance, improving high-frequency response.

- Active Control Circuits: Using pulse drivers or current sources to rapidly change bias conditions can enhance switching speed by an order of magnitude.

5. Applications and Future Trends

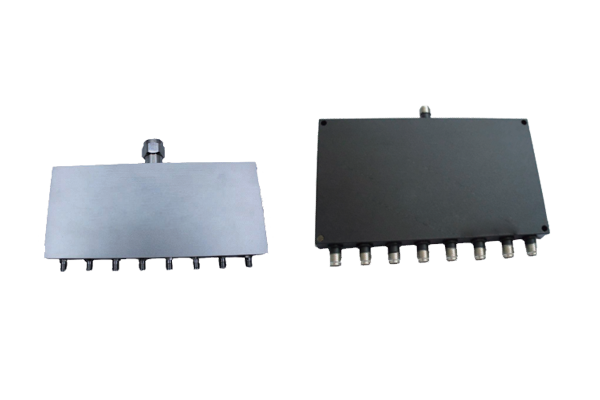

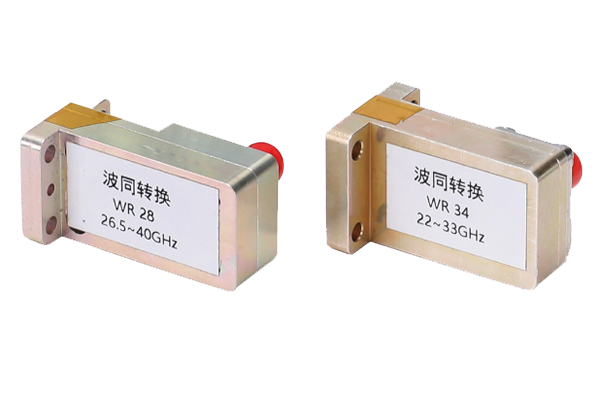

Require sub-nanosecond to nanosecond-level speed for agile signal routing (e.g., phased-array antennas).

Slower switches (microsecond range) are acceptable for low-frequency power control but face competition from MOSFETs/IGBTs.

Ultra-fast PIN diodes with graphene or silicon carbide (SiC) substrates may push response speeds into the picosecond range while improving thermal stability.